RTDX Interfacing and Testing II

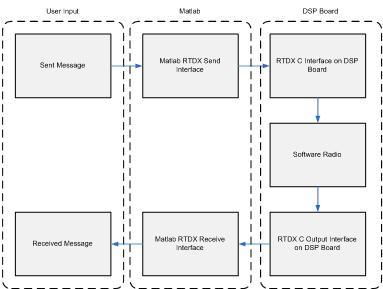

Now that the receive RTDX blocks in Simulink are verified to work and experience has been gained in working with RTDX, Matlab, and Code Composer Studio, we need to design a test system that will verify that the Software radio parts are working as intended on the board. The first thing that needs developed when doing this is a block diagram of the radio. This is shown in Figure 1.

Figure 1 - Block Diagram for Software Radio Test Interface

The Matlab program will act as the bridge between the user and the DSP board. It will take the users message, convert the message into a binary stream, transmit it to the DSP board, and indicate to the DSP board that the data is ready to be sent through the radio. On the receive side, the Matlab program will do the opposite. It will wait until DSP indicates that the radio is done processing the data, receive this data into Matlab, and then convert it back into the form of the original message.

On the DSP side, two simulink blocks/sections of C code will interface the RTDX to the software radio designed in simulink. The Input interface block waits until the data has been sent by the Matlab program, the data is put in a convenient location for the Simulink program to process and indicate to the radio that it has data to process. After this, the radio will process the data. The output interface block will stop the radio when its buffer is full and indicate to the Matlab program that the processing has been completed, and transmit the data back into Matlab.

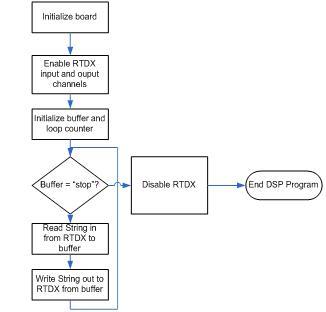

To test the interface, a program will be developed to run on the DSP board. A simple echo program was designed in C to echo back whatever string came in the input of the DSP board. The code from this program will later be used to implement the testing blocks in simulink. A flow chart for this program can be found in figure 2.

Figure 5 - Flowchart for test echo DSP program

Karl on 01.19.06 @ 06:56 PM CST [link] [No Comments]

Thursday, January 11th

RTDX Interfacing and Testing I

The RTDX interface in Simulink was investigated to verify the transfer of data to and from the DSP board when testing the software radio. RTDX is a way to programmatically send and receive data to and from the TI 6713DSK board through code composer studio. Although the interface will not work in a production environment, it is an excellent way to send data to the DSK board for testing.

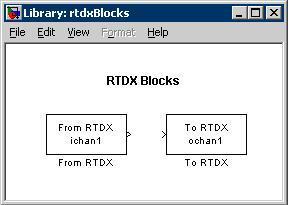

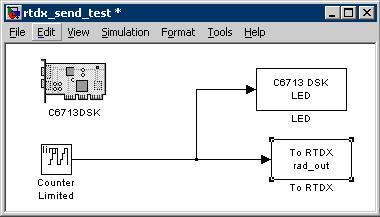

Figure 1 - RTDX Blocks in simulink

The From RTDX block receives data from the host PC and transmits that data to the DSK board. The To RTDX block transmits data from the DSK board to the Host PC.

As a starting point for testing, the model in figure 2 was created.

Figure 2 - Test model for RTDX data tranmission from DSK to PC

The model counts from 0 15, incrementing every 1 second and transmits this to the RTDX channel. This value is also sent to the LEDs so that there is a visual indicator on the board that it is still running the program.

Communication on the host side was programmed in Matlab. The Code Composer Studio link for Matlab provides functions for interfacing with RTDX.

When receiving an RTDX message in matbab, there are 3 things one needs to first do:

1. Enable RTDX overall

2. Open the specific RTDX channel.

3. Enable the specific RTDX channel.

Once this takes place, the board will begin to transmit the data to code composer studio. When the connection is not enabled, the messages are lost. The message is then read with the readmsg function. After the data is taken in, the channel is then disabled, closed, and rtdx itself is disabled.

Karl on 01.11.06 @ 03:42 PM CST [link] [No Comments]