# Senior Project Design Review:

## Internal Hardware Design of a Microcontroller in VLSI

Designers:

Shreya Prasad & Heather Smith

Advisor:

Dr. Vinod Prasad

March 11th, 2003

## **Presentation Outline**

- Project summary

- Review of preliminary work

- Project description (by subsystems)

- Functional description

- Block diagram

- Schedule of tasks

### Project Summary

•To design some of the internal components of a microcontroller using L-EDIT.

•To create several delays by designing the internal 16bit timer circuitry and 4 registers.

• These delays can run real time systems and interrupts.

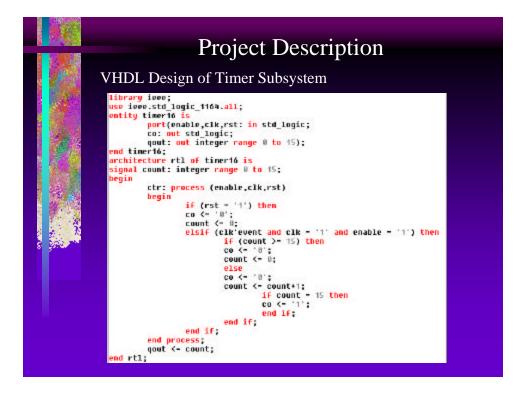

•The design will also be done in VHDL code and implemented into FPGA.

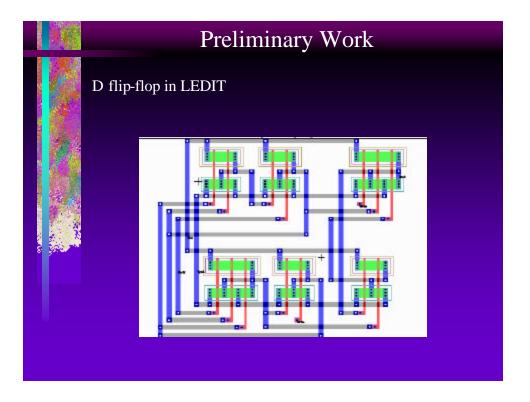

### **Preliminary Work**

•The microcontroller to be designed is similar to the Motorola 68HC11.

•The designers used Motorola's microcontroller as a guide; however, their logic design was independent.

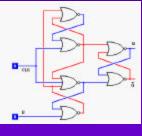

•*http://www.play-hookey.com* helped the designers with the gate level design for the D flip-flop and the XOR gate.

•The D flip-flop designed used the least number of gates.

**Functional Description**

#### **User inputs:**

- •8-bit accumulator

- •2-bit register controller input and 1-bit enable

- •2-bit clock controller input and 1-bit enable

- •timer reset

- •clock

#### **User outputs:**

- •1 bit from each of the four comparators

- •1 bit overflow from timer

#### **Project Description**

#### **Functional Description**

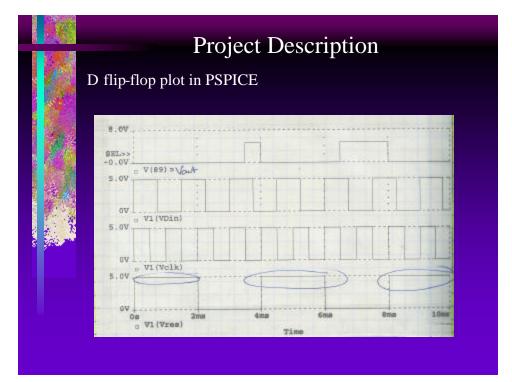

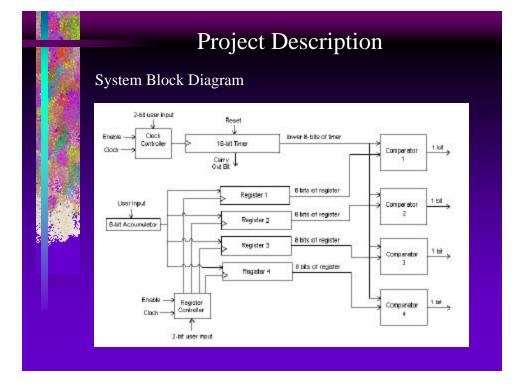

**Modes of operation:** The user inputs 8 bits into the accumulator and 2 bits to the register controller and clock controller. The register controller specifies which register to store the 8 bits into. The clock controller specifies the period of the input clock pulse.

The 16-bit timer continuously increments with the clock. The lower 8 bits input into each of the 4 comparators. They are then compared to the 8 bits stored in each register. The comparator output is logic '1' when the two values are equal.

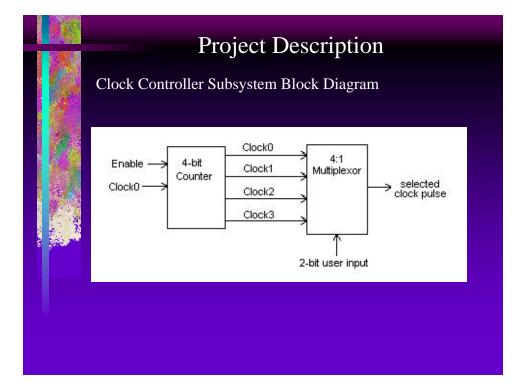

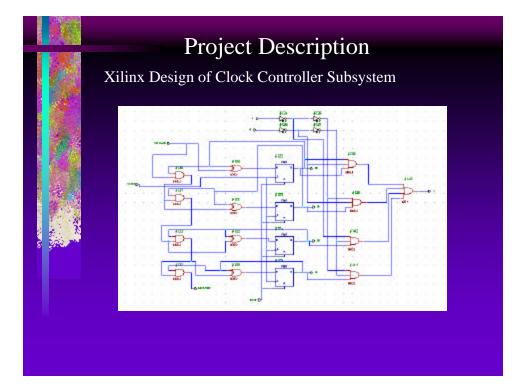

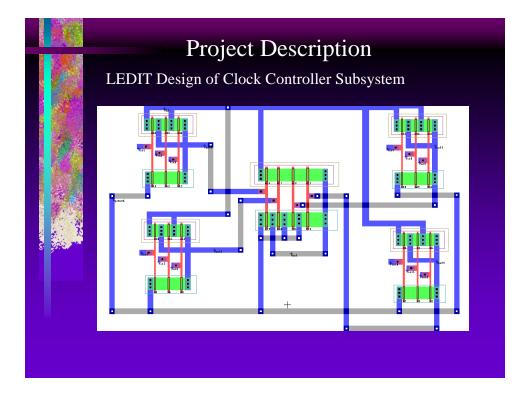

Description of Clock Controller Subsystem

•This controls the clock pulse entering the timer subsystem.

•The user inputs the fastest clock pulse desired into the clock input.

•The subsystem can then output that pulse, or a pulse two times, four times, or eight times the period of the original pulse, into the timer subsystem.

•The 2-bit controller value selects which pulse to output using a 4 to 1 multiplexer.

•The pulse periods are decreased using a 4-bit counter.

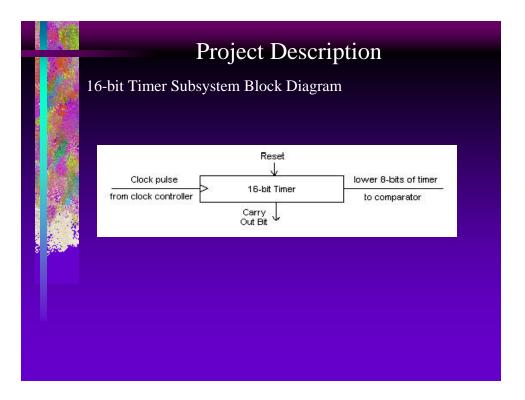

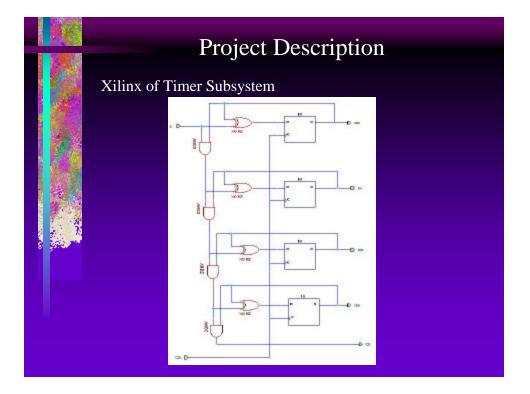

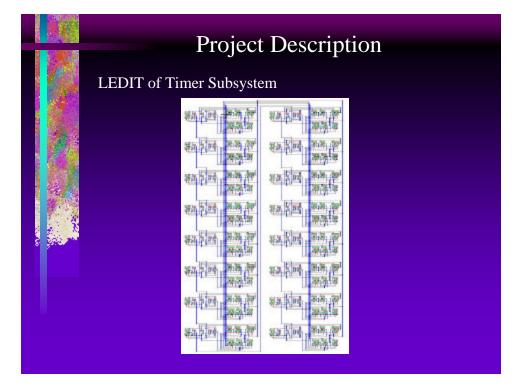

|     | Project Description                                   |  |  |  |

|-----|-------------------------------------------------------|--|--|--|

|     | 16-bit Timer Subsystem                                |  |  |  |

|     | Inputs:                                               |  |  |  |

|     | Clock (from clock controller subsystem)               |  |  |  |

|     | Enable (user input)                                   |  |  |  |

|     | Reset (user input)                                    |  |  |  |

| A R | Outputs:                                              |  |  |  |

|     | Lower 8 bits of timer value (to comparator subsystem) |  |  |  |

|     | Overflow bit (external output)                        |  |  |  |

|     |                                                       |  |  |  |

|     |                                                       |  |  |  |

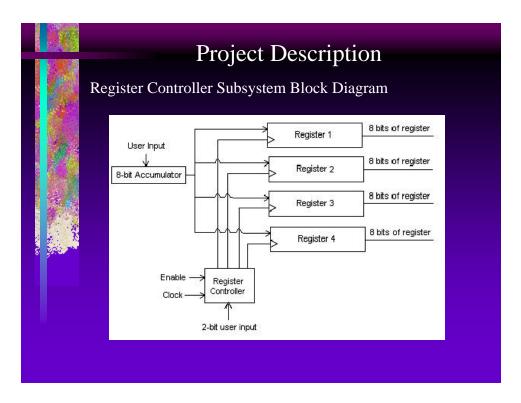

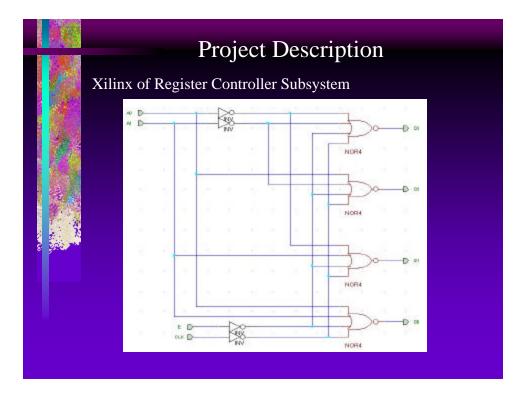

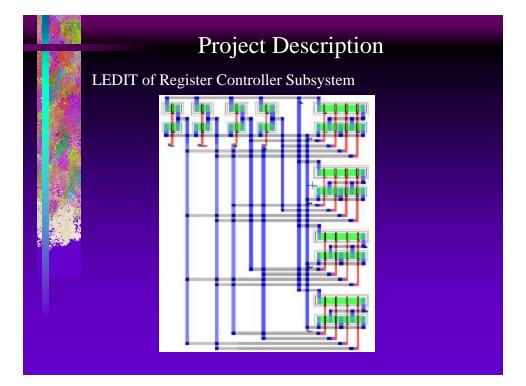

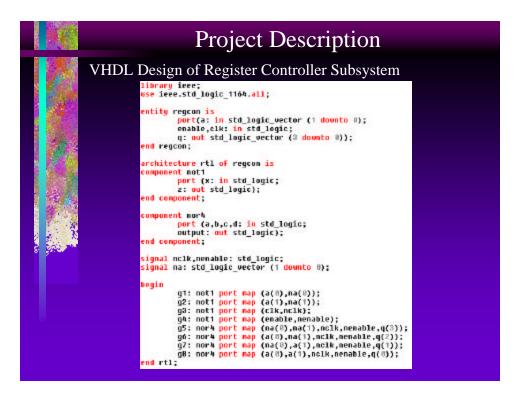

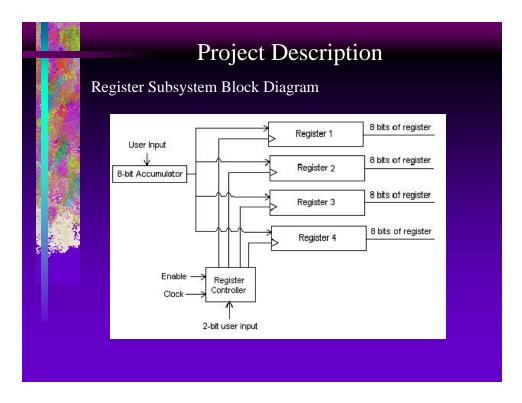

Description of Register Controller Subsystem.

•The 2-bit controller value specifies which of the 4 registers to point the 8-bit accumulator value to.

•A register only receives the accumulator value when the controller turns its clock on.

•Only register clock can be on at a time.

•A 1 to 4 decoder is used to select which register will receive the input clock pulse.

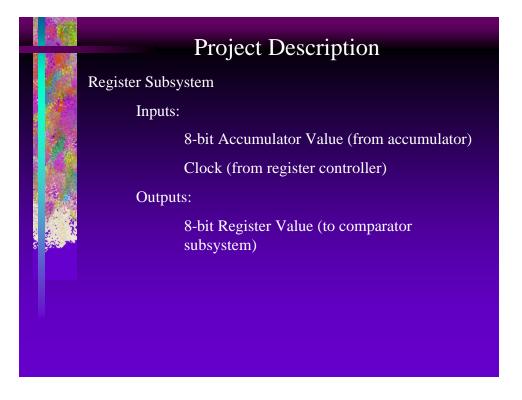

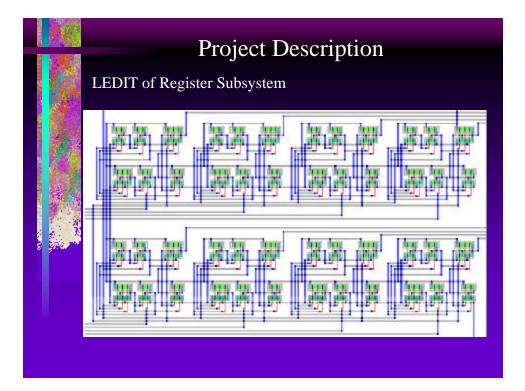

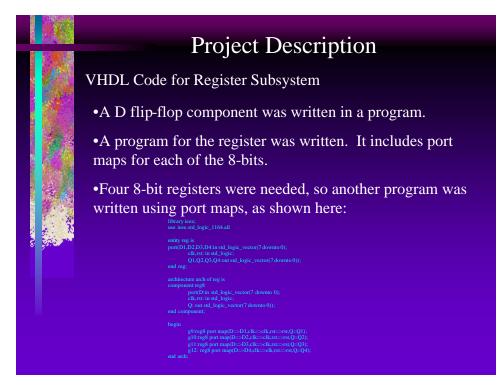

Description of Register Subsystem

•Each register will consist of 8 D flip-flops, which will store the register value.

•A register stores the accumulator value only when the controller turns on its clock.

•Otherwise, the register will hold its previous value until this value is written over with a new value from the accumulator.

•The inputs and outputs previously mentioned are for each of the 4 registers.

|   | Project Description<br>Comparator Subsystem Block Diagram |

|---|-----------------------------------------------------------|

| s | 8 bits from timer<br>Comparator N 1 bit output            |

|   |                                                           |

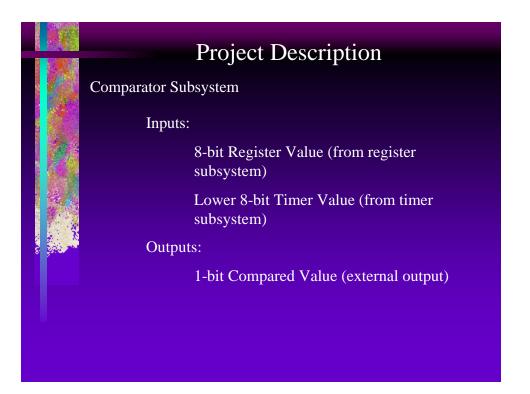

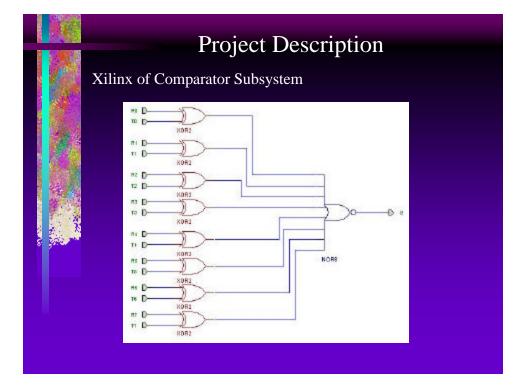

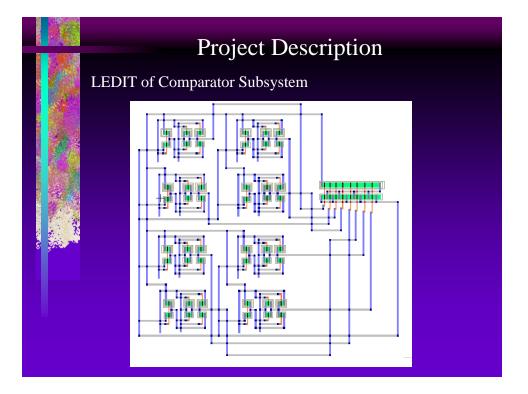

Description of Comparator Subsystem

•There are 4 comparators, 1 for each register.

•The 8-bit value from each register is compared to the lower 8-bits of the timer.

•If the two inputs are the same, the output is logic '1'.

•Otherwise, the output is logic '0'.

VHDL Code for Comparator Subsystem

•An XOR gate was written in a program.

•A NOR-8 gate was written in a program.

•The comparator program declared xor\_gate and nor8\_gate as components. Port maps were used as

#### shown below:

entity comp is port(r,t: in std\_logic\_vector(7 downto

rchitecture sgp of comp is omponent xor\_gate is ort(a,b: in std\_logic; :out std\_logic); nd component; component nor8\_gate port(input: in std\_logic\_vector(7 downto 0); output:out std\_logic); end component;

gnal s: std\_logic\_vector(7 downto 0); egin

g2:xor\_gate port map(r(1),(1),s(1)); g3: xor\_gate port map(r(2),(2),s(2)); g4: xor\_gate port map(r(3),(3),s(3)); g5: xor\_gate port map(r(4),s(4)); g6: xor\_gate port map(r(1),(5),s(5)); g7: xor\_gate port map(r(6),(6),s(6)); g8: xor\_gate port map(r(1),(1),s(7)); g9: ros@\_gate port map(r(2),x(2);

sgp

|          | Schedule of Tasks                       |           |                     |                 |  |

|----------|-----------------------------------------|-----------|---------------------|-----------------|--|

| 8 2 C    | Description                             | Completed | Partially Completed | Not yet started |  |

|          | Design Clock Controller in XILINX       | Х         |                     |                 |  |

| 32       | " in LEDIT                              |           | Х                   |                 |  |

| 100      | " in VHDL                               |           |                     | Х               |  |

|          |                                         |           |                     |                 |  |

| 100      | Design 16-bit timer in XILINX           | X         |                     |                 |  |

| 1997     | " in LEDIT                              | X         |                     |                 |  |

| 10.00    | " in VHDL                               |           | X                   |                 |  |

|          | Design Register Controller in XILINX    | v         |                     |                 |  |

|          | " in LEDIT                              | X         |                     |                 |  |

|          | " in VHDL                               | X         |                     |                 |  |

|          |                                         |           |                     |                 |  |

| 1.1      | Design Register in XILINX               | X         |                     |                 |  |

| a > b    | " in LEDIT                              | Х         |                     |                 |  |

| 1940 Mar | " in VHDL                               | Х         |                     |                 |  |

|          |                                         |           |                     |                 |  |

|          | Design Comparator in XILINX             | Х         |                     |                 |  |

|          | " in LEDIT                              | X         |                     |                 |  |

|          | " in VHDL                               | X         |                     |                 |  |

|          | Combine subsustance in VII INV          |           | v                   |                 |  |

|          | Combine subsystems in XILINX " in LEDIT |           | X                   |                 |  |

|          | " in VHDL                               |           | ^                   | Х               |  |

|          |                                         |           |                     | ~               |  |