This senior project focuses on the idea of data encryption, more specifically the design of a VLSI encryption system. The model of this system is based loosely on the form currently being used in automated teller machines (ATMs). These machines use a 12-bit polynomial encryption program to protect and encrypt the information that the ATM user is providing into the system. This encrypted signal is then sent to the proper computer for decryption, further analysis, and response.

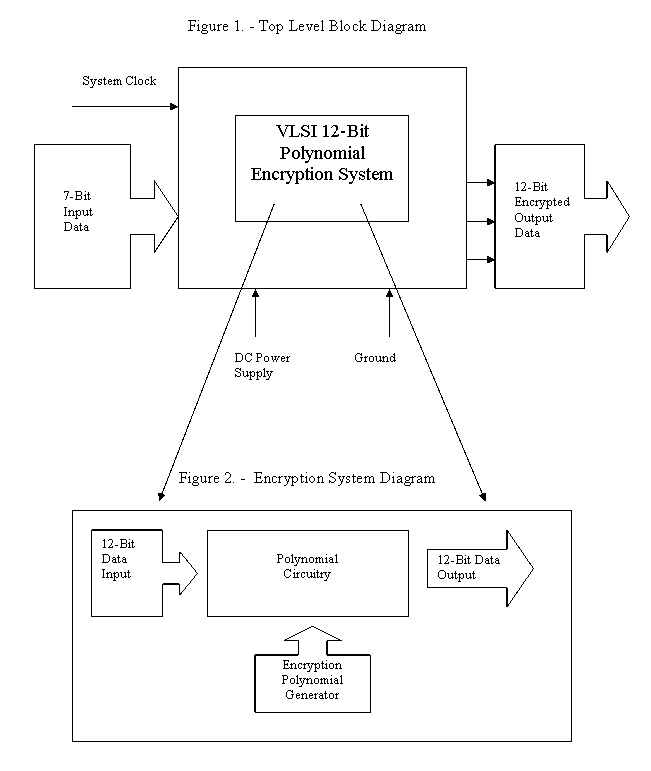

The

senior project will be to design a single system that will be able to encrypt a

7-bit data input (four bits code word, three bits of parity), using a complex

polynomial function generator, and output a 12-bit encrypted signal (see Figure

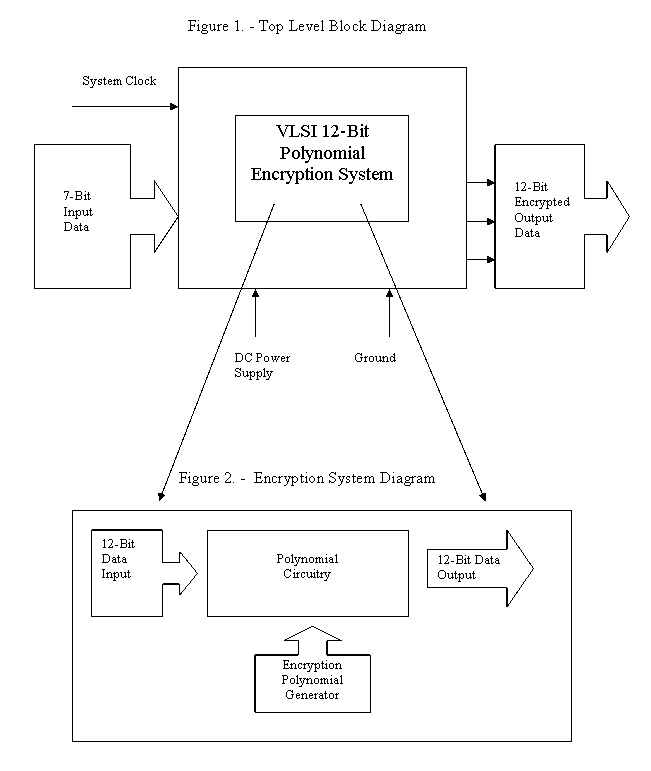

1). This function generator takes a seemingly random polynomial, and multiplies

it with the input (see Figure 2). This new set of data is now the encrypted

signal, and is sent to the proper receiver. The polynomial multiplier is

hardwired into the system as a series of network logic, all of which will be

designed using VLSI techniques. The design process will continue to the

point where the system will be able to be physically fabricated in a single

chip. The only mode of operation for this chip is a continual encryption

of the input data.

Assuming

time allows, a form of testability will also be designed and implemented for

this system, either using test vectors or a similar method. The data being

transmitted will have a certain number of parity bits incorporated to ascertain

the correctness of the signal.